FPGA Verification

EnSilica provide a comprehensive range of FPGA verification services to reduce the time to market and improve the quality and reliability of your product.

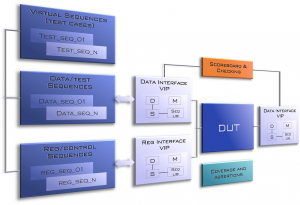

Verification represents one of the biggest challenges facing FPGA teams getting their design into the market within acceptable timescales. Many teams get stuck for months testing product in the lab rather than simulating using self-checking test benches.

This is where EnSilica verification consultants can help. We understand the challenges presented by these designs and work with our customers to provide everything from in-depth knowledge to solve a specific verification problem, to delivering a comprehensive verification solution to meet your commercial and technical needs.

For high reliability or safety critical applications, EnSilica has experience in developing executable verification plans with requirements tracking for automotive products using ISO26262, avionic control systems to DO254 and industrial or oil/gas systems to IEC 65108.

EnSilica use code and functional coverage to measure the completeness of the verification, we can also apply formal tools to improve the coverage and check for unreachable or dead code.