EnSilica's news hub

Latest Posts

EnSilica to exhibit at TSMC 2026 NA Technology Symposium in Santa Clara

Join us EnSilica at TSMC 2026 NA Technology Symposium on 22 April!

Silicon innovation is expanding AI to ...

EnSilica selected for UK CHERI Adoption Collective

Part of a leading team of companies to address the UK's £27bn cyber resilience problem

EnSilica is pleased ...

EnSilica to exhibit at SATShow 2026

We are very excited to be part of SATShow 2026!

Come and speak with our experts to discover how ASIC solutions ...

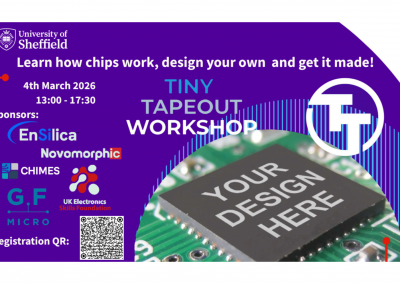

EnSilica to sponsor Tiny Tapeout workshop at the University of Sheffield

We are proud to announce that EnSilica is supporting a hands-on ASIC design workshop at the University of ...

EnSilica to exhibit at AutoTech 2026

We are very excited to be part of AutoTech 2026!Come and speak with our experts to discover how ASIC solutions can ...

How EnSilica Supports Brazil’s Growing Semiconductor Ecosystem

Brazil’s semiconductor ambitions are accelerating – and EnSilica is part of that story. The country is investing ...

EnSilica will be presenting its latest Satcom ASICs soultions at MWC26

EnSilica will be showcasing its latest Satcom ASIC developments at Mobile World Congress 26 in Barcelona.

The ...

EnSilica to exhibit at Embedded World 26

We’re excited to share that EnSilica will be exhibiting at Embedded World 2026 Nuremberg, Germany

10–12 March ...

Electrocardiography ADC architectures, trade-offs and use cases

The ideal balance of power, resolution and accuracy in ECG systems depends strongly on the intended use ...

No results found.

Just tune in

Podcast

The Economics of Custom ASICs- Viability Analysis

ASIC for differentiation

Articles

Articles by EnSilica’s employees published in leading industry titles

A CHERI on Top: A Better Way to Build Embedded Secure SoCs

embedded.com

Why turnkey ASICs are regaining strategic importance in embedded innovation

Electronic Specifier Magazine

The importance of ADCs in low-power electrocardiography ASICs

Medical Journal

Electrocardiography ADC architectures, trade-offs and use cases (Dec 2025)

medicaldesignandoutsourcing.com

Just a Tap: NFC’s Role in Smarter Healthcare Devices

EE Times

No results found.