NEWS UPDATE

Article first published in EET Asia on 19th May 2021; by Ian Lankshear, Managing Director EnSilica.

The economics of 8in wafers make the current supply shortages a feature, not a glitch. Shifting to 12in can help future-proof your supply chain.

To put it mildly, the 8-inch (200mm) wafer supply chain is somewhat struggling.

As one headline from December read, “8-inch wafer capacity is in short supply to unimaginable levels”, with the article stating “wafer production capacity is so tight that customers’ demand for production capacity has reached a panic level.” And that from mid 2021 “to the second half of 2022, the logic and DRAM markets will be out of stock.”

This is not a new problem, Trends Force stated around the same time that “8-inch wafer capacity has been in severe shortage since 2H19”. And EE Times reported in February 2020 that “Shortages loom after 8-inch fabs run at 99% capacity in Q1”.

And to cap it all off, March’s fire at a Renesas fab used by GM and other car manufacturers can only make matters worse. As Nikkei put it: “Loss of advanced semiconductors could worsen global crunch [of automotive chips].”

The causes of these issues are multiple, but have been hugely exacerbated by the pandemic, which has driven demand for many types of products including headphones, PCs, TVs, monitors and mobile phones. Added to this are sectors such as automotive which were expected to begin recovering from the Pandemic this year. And whilst products aim to integrate many functions into a single SoC, many products typically have a digital IC accompanied by one or more mixed-signal companion chips. These cover applications such as power management (PMIC), CMOS image sensing, fingerprint sensing, automotive motor and chassis control, display drivers and sub-GHz RF radios and typically make use of 180 nm or 350 nm technology, manufactured on 8-inch (200mm) wafers.

In short, the continuous increase in demand for these mixed signal chips and power devices is the main reason for the shortage of 8-inch wafer production capacity.

With 8-inch wafer supply at breaking point, it might be assumed foundries would be adding capacity. And foundries are looking to acquire 8-inch manufacturing lines and equipment from IDM’s, one recent example of this is UMC reportedly being in talks to acquire 8-inch lines from Toshiba.

Fig 1: TSMC supplies 12” wafers for 130 nm processes and smaller. 8” wafers are used for 130 nm and larger. Note, 130nm processes can be supplied in both 8” and 12” wafers.

But, as per the above TrendsForce report, the severe shortage since 2H19 can be attributed to there being “almost no suppliers still currently produc[ing] 8-inch semiconductor equipment, meaning the price for such equipment has now skyrocketed. Moreover, since 8-inch wafer prices are relatively low in comparison to 12-inch wafer prices, foundries generally find it cost-ineffective to expand their 8-inch capacities”. And this has a knock-on effect, with some foundries raising their 8-inch wafer prices to customers.

To put another way, the economics of 8-inch wafers make these shortages a feature of rather than a glitch in the supply chain.

And the situation will not improve. Unlike with 12-inch (300mm) foundries where there are many announcements regarding further investment in capacity – notably from TSMC and from GlobalFoundries.

Given the likelihood that there will not be further 8-inch capacity, some IC suppliers are migrating their existing designs from 180 nm and 350 nm 8-inch lines to newer lines using 12-inch wafers. And many foundries provide suitable 130 nm processes manufactured on 12-inch wafers, which can be used as a second or main source to service future capacity needs; and add geographic diversity in the supply chain.

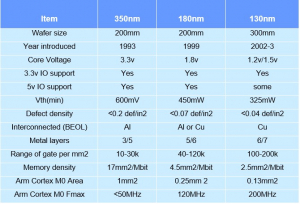

Properties of 180 nm vs 130 nm process nodes

Even between similar process nodes such as 180 nm and 130 nm, they have different properties. The key being the different transistor threshold voltage level dropping, in line with the reduction in the core supply voltage from 1.8 V to 1.5 V or even 1.2 V. Various process options are available to support 5 V and 3.3 V IOs, and the passive components offered, essential for analogue and RF design, are similar between these process nodes.

Fig 2: A comparison of main nodes used for mixed-signal ASICs

The 12-inch technologies offer some advantages. They generally use copper for metal interconnects, whereas higher resistivity aluminium is used in older technologies, which allows higher current densities and protection against electromigration. The 12-inch technologies also support a larger number of metal layers and this, combined with the smaller transistor dimensions, allows an increase in the transistor and routing density and so a reduction is the die area or an increased functionality for a given unit price.

In addition, many 180nm and most 130nm BCD (Bipolar-CMOS-DMOS) technologies support features such as shallow trench isolation (STI) for higher density, improved latch-up protection and substrate noise isolation compared to the Local Oxidation of Silicon (LOCOS) isolation used in most 350nm technologies. These will improve the performance and robustness of the circuits.

The improved lithography used for the newer 12-inch wafers offers better device matching for improved the manufacturing yield. Again, supporting lower price per good die.

Additionally, 130nm BCD nodes are now very mature technologies that offer many more process options, including different high voltage classes of transistors, non-volatile memories (OTP, flash), MIM caps, zener or schottky diodes, etc. This can benefit the integration of complex analog/RF functions into a more competitive SoC solutions.

Cost vs supply chain stability

That’s not to say there aren’t reasons to stick with 8-inch wafers. Millimetre for millimetre, 350 nm 8-inch wafers have been cheap, dirt cheap.

This is because the manufacturing equipment is fully depreciated and there being a low complexity of the manufacturing process (small number of layers). Additionally, some analogue circuits do not always scale so well in newer nodes, and 130 nm equivalent chips can therefore be more expensive than your 350nm. However, in most cases the inability to supply your product (be it a pair of headphones, a mobile phone, or a car) due to component shortages, will cause more pain than a small cost delta in your IC.

Furthermore, designing a pin-to-pin compatible device with matching electrical parameters can be challenging when moving across nodes due to different supply, IO voltage support and different transistor characteristics. Each design would need to be analysed to confirm it was possible and did not add significant overhead, which could be more easily overcome by making a new PCB design. It should be noted that the gap in bridging 180nm to 130nm is less of a leap than going from design in 350nm to 130nm.

It is also worth noting at this point in the discussion that there is no talk at this time by the foundries of them migrating 180 nm 8-inch design kits to 12-inch lines. Skilled mixed signal ASIC houses (like EnSilica) are going to need to do this work starting with either a schematic level port or from the IC datasheet.

Implications

Given the investment that is required to re-design an ASIC, it would be advisable to look at integrating other features that also might be in affected by 8-inch supply chain issues, particularly the MCU.

The smaller feature size of 130nm would allow the integration of Arm Cortex M class processors with little extra silicon cost. Indeed, the required CPU performance and memory requirement will be the dominating factors on the viability of integration; with just a couple of square millimetres of silicon area required for a low-end CPU, and a few more allowing 64/128 kB of SRAM to be integrated cost effectively.

For non-volatile memory OTP, MTP and Flash are often available, giving a performance of a couple of hundred MHz, which is normally sufficient for most of these types of application. If using the Cortex-M0 or Cortex-M3, which are usually a good fit when targeting 130nm, a place to begin is the free of charge (per part royalties only) tool Arm Flexible Access.

The schedule to redesign an ASIC from its current datasheet and be qualified ready for production would be in the order of 14 to 24 months depending on the complexity, first prototype silicon could be with you in less than a year. For automotive products from specification to PPAP would be more like 24 to 36 months, again depending on the complexity. Typical budgets for a 130 nm ASIC would vary depending on the design complexity and IP licensing content but begin at c.$600k, stretching to c.$4M for a full AEC-Q100 qualified component for automotive applications. The cost of 130 nm mask tooling on a 12-inch process is now below $200k so relatively small part of the overall cost.

Conclusion

Many mixed signal devices are manufactured on 8-inch wafers that are in short supply and lack of investment (caused by a low return on investment) in these manufacturing lines means supply-chain issues are likely to continue.

The current shortages should be seen as a warning and companies currently using silicon on 8-inch wafers should prioritise a review their future demand. If it requires significant capacity, then they should consider porting to a 12-inch node and allow enough time for the whole process to be completed – be it at the main, or the second source production facility.